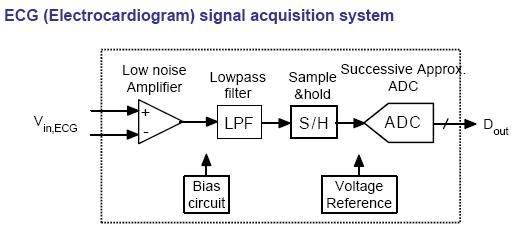

My part is going to be the ADC, which is quite challenging I would say. The architecture of this ADC is to be using the successive approximation algorithm, while my FYP is on another kind of architecture called the sigma delta modulation, which makes use of oversampling and noise shaping technique. From what I see now, both designs are quite hard one. Moreover, the dateline for the submission of the EE4410 final design is in week 9. This means the schematic design as well as the layout design to be ready for tape out. So, we have only around 2 months to complete this, which is really really rushed. I am so going to relive the days of EE2001 and eat, work, sleep on EE4410 everyday. Wait, there’s also my FYP hor? Wah, means eat, work, sleep on EE4410 and EE4001, like doing 2 FYPs.. Great, just great…

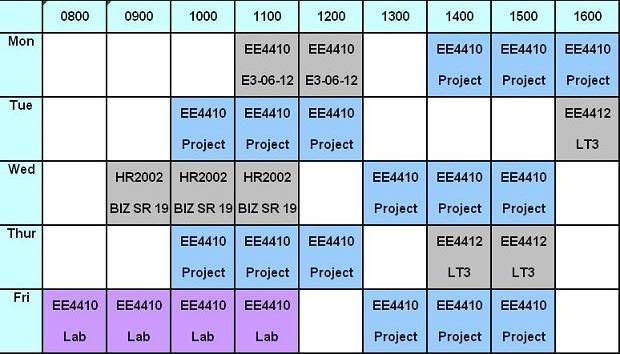

Now, some people went a bit crazy over the fact that my timetable in my previous entry was like so empty. Well, now to loosen them up a bit, here I posted another timetable which will very likely quite accurately reflects what I will be working on for the next month or so. It seems preposterous somewhat, but that’s really what my group intended to do. Complete the design by mid term and start worrying about our FYP.

Wish my good luck, will ya?

5 comments:

now, your time table looks more like it.

good luck~

chionggggggggg

haha.. good luck.

lol

Jiayou! :)

Thanks all! =)) haha

Post a Comment