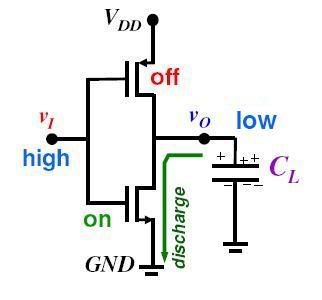

(For those who are not familiar, the picture to the left is a CMOS inverter and is equivalent to a NOT gate. Basically, it inverts the input signal.)

(For those who are not familiar, the picture to the left is a CMOS inverter and is equivalent to a NOT gate. Basically, it inverts the input signal.)Nus exams are like CMOS inverters. Go in with high confidence, but during the operation discharged all my charges and pull my confidence signal down to ground. So end result is a low confidence level for the output.

Perhaps next time should try to go in with low confidence. Then I will be charged up and subsequently can pull my confidence signal up to Vdd. Then got high output. Perhaps my switching speed from low to high wasn't fast enough. Maybe i should have increased my width (W) and reduced my length (L), since t(PLH) is inversely proportional to (W/L). Ok I am losing it...

7 comments:

hey hey don't lose it yet. still got 4 more battles to fight. cannot attend c hor.

Also, you haven't seen enough of NOT gates this sem. You shall have LOTS of fun playing with LOTS of not gates next sem, haha...

I think the propagation delays added up, so the max frequency is limited as a result. Maybe should use ROM instead of MOSFET, ROM faster, higher density but just needs more power.

chill dude. ur not the only one. sigh

you need a full-wave rectifier..

Told ya life was and is hard. So,

HARD LIFE LAR.

hey dude. same sentiments here.

haha.. go in with confidence and come out feeling so deflated.

sigh!

Naka:

Oh my, logic gates.. they are quite fun, aren't they? (Have to deceive oneself sometimes to make life easier ya?)

Chuwen:

Cannot lar, too much power consumption means brain voltage higher, later device malfunction sia.

Don:

Yea, may the power of moderation be with us!

Chillycraps:

Yea, if only device is always on high mode! =(

Ninja:

Ya lar hard life lar.

Fabian:

Heh, dun worry, believe in the powers of moderation!

Post a Comment